HW Implementation of Computer Vision Algorithms for Autonomous Rover Navigation (ESA ExoMars Mission)

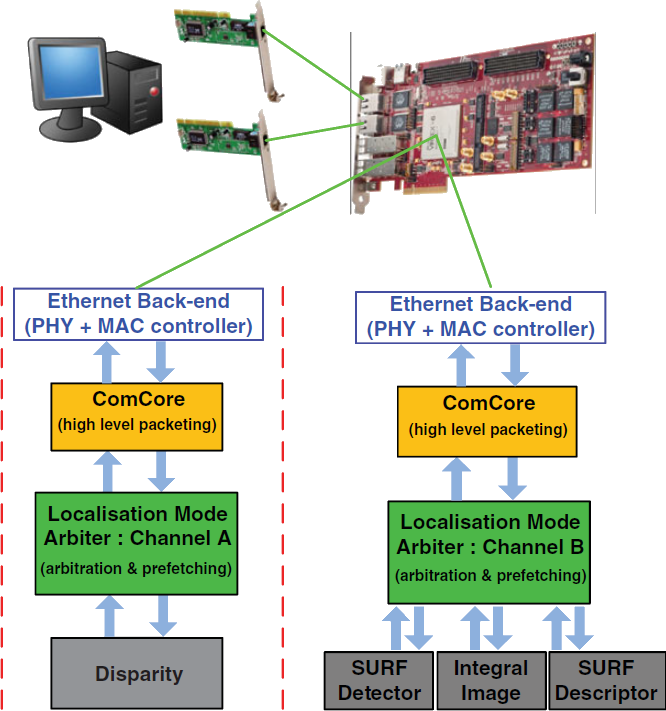

Mars exploration is expected to remain a focus of the scientific community in the years to come. A Mars rover should be highly autonomous because communication between the rover and the terrestrial operation center is difficult, and because the vehicle should spend as much of its traverse time as possible moving. Autonomous behavior of the rover implies that the vision system provides both a wide view to enable navigation and three‐dimensional (3D) reconstruction, and at the same time a close‐up view ensuring safety and providing reliable odometry data. This work deals with the physical design of rover’s vision system onto Xilinx Virtex-6 FPGA board.

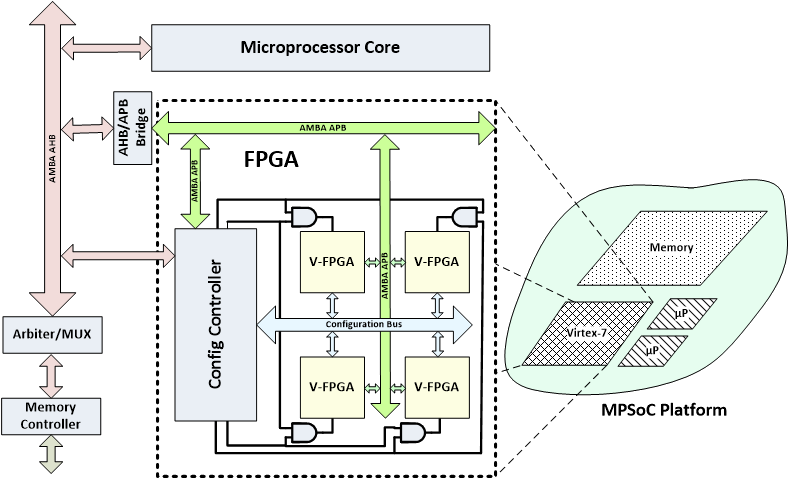

Virtual FPGA Platform

The virtual FPGA (V-FPGA) architecture is an island-style FPGA described in reusable VHDL and mapped onto Alter Stratix FPGA devices. V-FPGA is realized as virtual reconfigurable hardware upon a traditional off-the-shelf FPGA device. Since the architectural properties (e.g., the LUT size and the number of LUTs per slice) of each V-FPGA are easily customizable at design time (through a graphical user interface) depending on the application’s requirements, the employed V-FPGA can be considered an optimized application-specific platform. The target platform includes also a microprocessor core, a configuration controller, some off-chip memories, and buses for on-chip communication and configuration. The programming of V-FPGAs is performed with CAD tools describe at the “CAD Algorithms & Tools for Physical Design” Section.

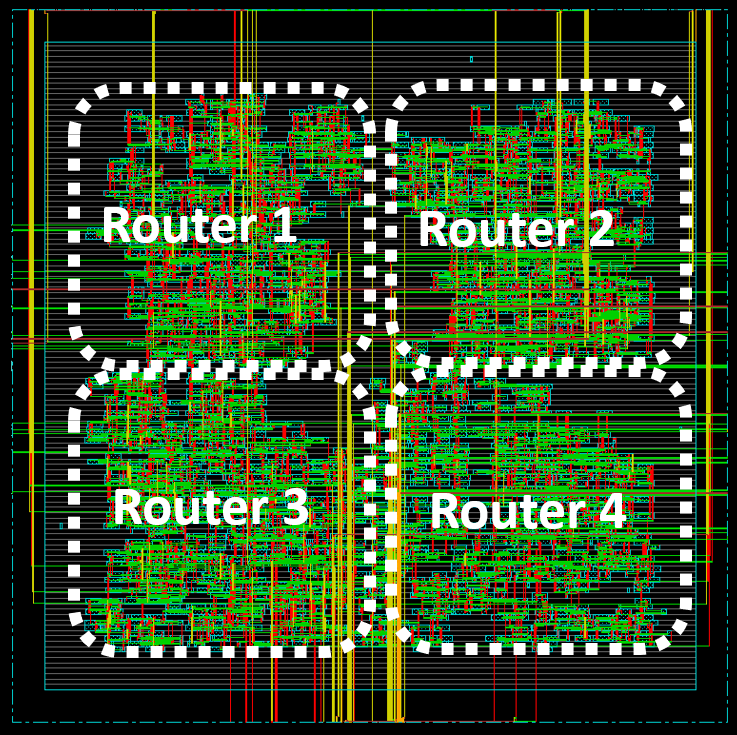

FLEXNOC: Reconfigurable Network-on-Chip (NoC) IP Core

Toolset for enabling the Design and customized Network-on-Chip architectures. The software produces in automated way the synthesable Hardware Description Language (HDL) for the instantiated NoC. Tasks related to architecture-level exploration and optimization are also addressed within this tool. The FLEXNOC IP supports:

- High-level topology exploration of NoC network

- Automated generation a reusable NoC architecture at RTL

- NoC customization in terms of routing algorithm (XY, LUT-based, …), number of router, selected topology (regular/irregular), buffer sizes, etc